What

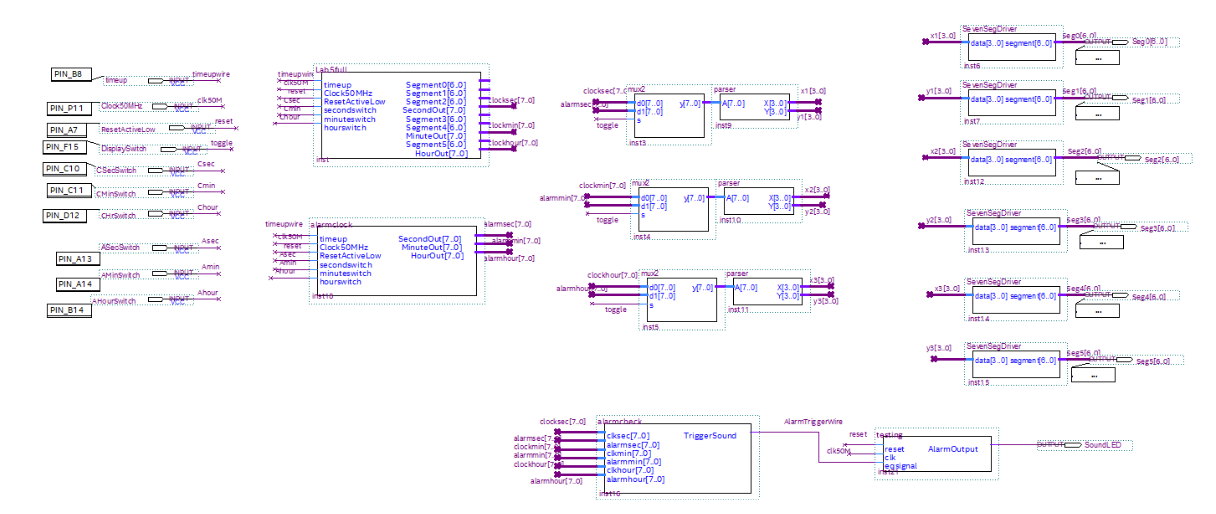

This project involved designing and implementing an alarm clock on an FPGA. The system allowed users to set the current time and alarm time, and when the time matched, a tone was played through an external speaker. The project was built using SystemVerilog for individual functional blocks, simulated in ModelSim, and connected using Quartus before uploading to the FPGA board.

How

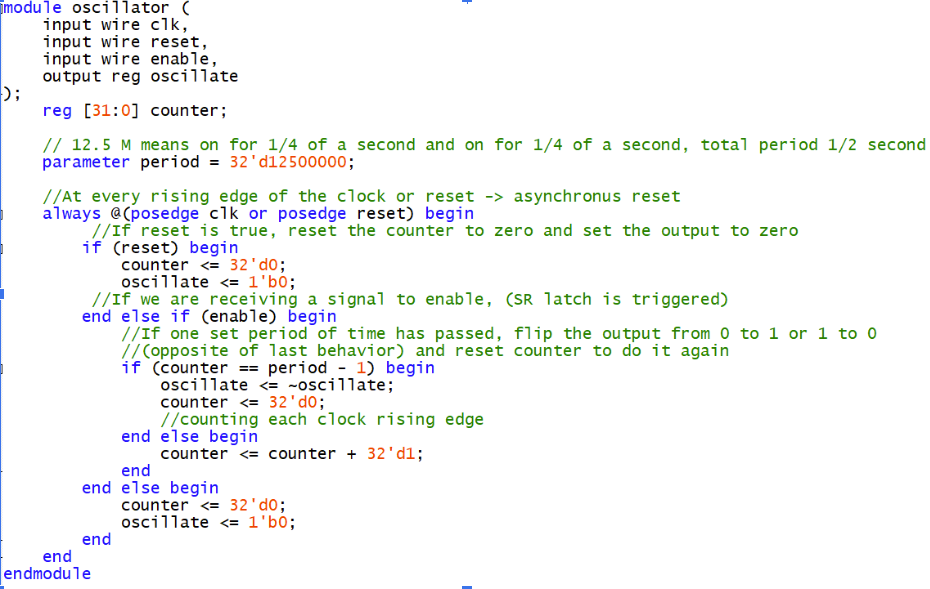

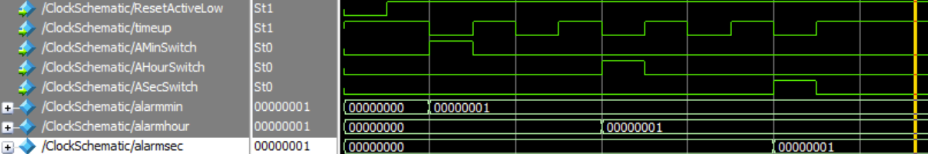

The project was developed by breaking the system into modular blocks in SystemVerilog. Key components included a clock counter, alarm comparator, and tone generator. Each module was verified through testbenches in ModelSim. The blocks were connected in Quartus using a top-level design, and the final program was uploaded to our FPGA (DE10-Lite) for testing with external inputs and outputs.

Reflection

This project improved my understanding of FPGA design, including modular development and verification. Challenges included debugging timing issues in simulation and ensuring proper synchronization of the alarm tone. Future enhancements could involve adding features like multiple alarms, adjustable tones, and a user-friendly interface with a digital display. This could incorporate a layered button menu similar to many watches on the market today, just 4 buttons that have different functionality depending on the menu.