What

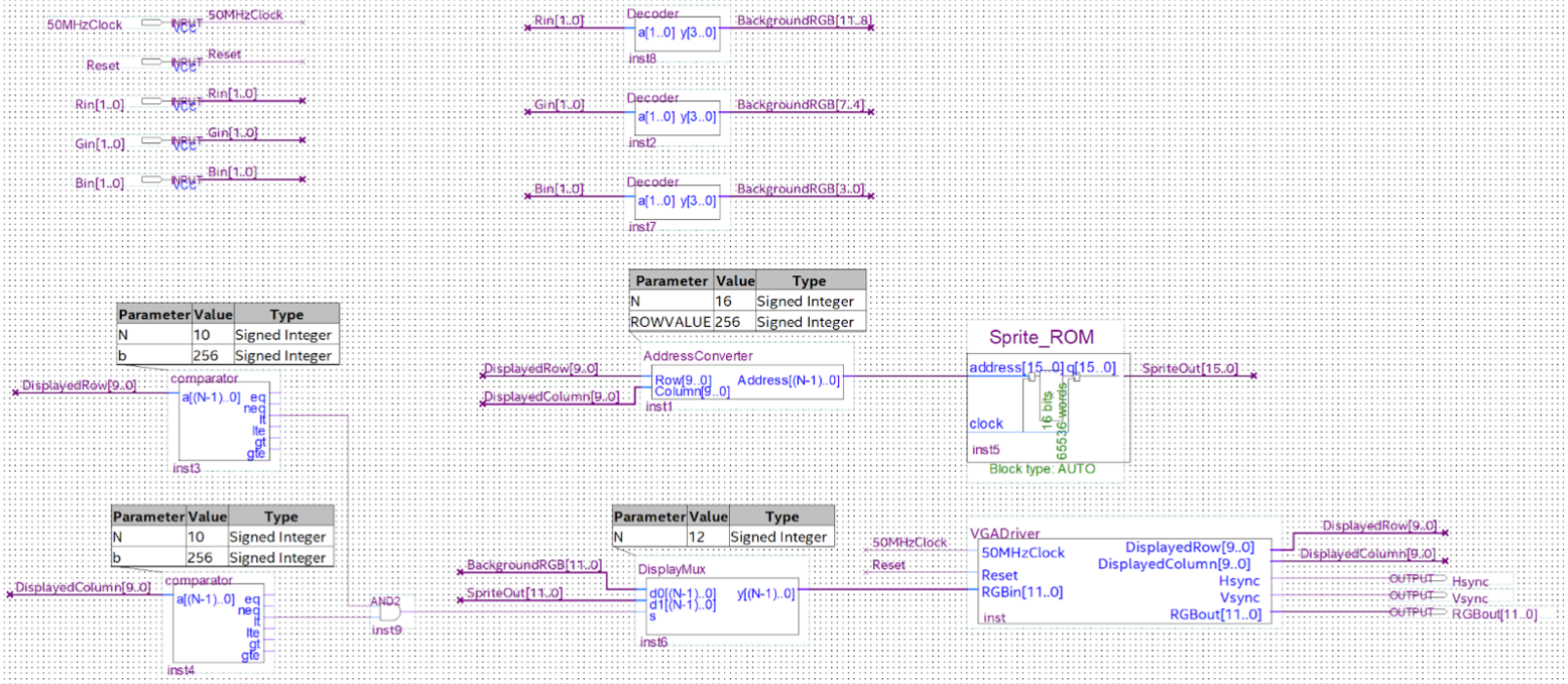

This was tasked to me in my digital logic lab where the goal was displaying a png on the display over VGA. This involved converting the png to a MIF file and designing the logic necessary to display the image pixel by pixel.

How

This project required using read only memory (ROM) to store the MIF and designing decoders and address converters to display the image in the correct part of the screen. This program was completed in Quartus and blocks were made in SystemVerilog.

Reflection

This assignment was very satisfying to complete as it felt very complex at the time and took lots of understanding to execute. One challenge I faced along the way was inverting the polarity of my mux which would determine if a certain pixel was part of the image or part of the background. Needless to say this caused lots of expected behavior and debugging and simulation in modelsim to catch and fix.